In diesem Teil des Tutorials möchte ich zeigen, wie das Two Wire Interface (TWI), ein I2C-kompatibler Nachbau von Atmel, eines XMega-Mikrocontrollers genutzt werden kann. Texas Instruments hat ein sehr schönes Dokument veröffentlicht, in dem die Funktionsweise des I2C-Bus sehr detailiert erklärt wird, falls es beim Verständnis des I2C-Bus noch die ein oder andere Lücke geben sollte.

XMega als I2C-Master:

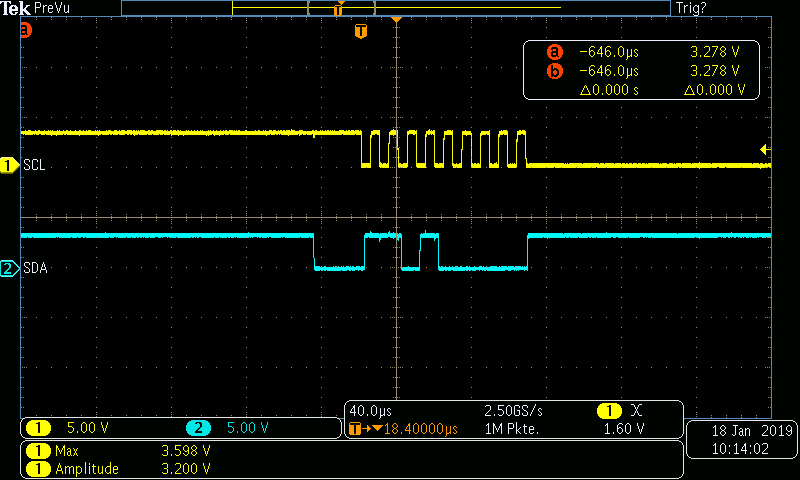

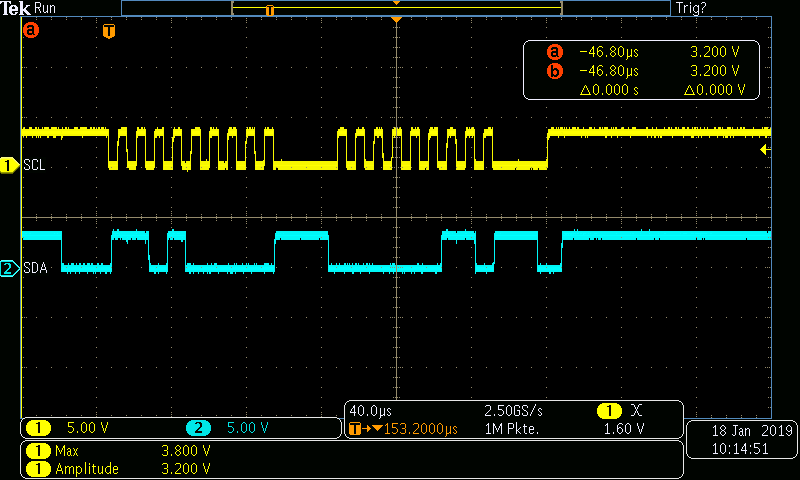

Den Anfang möchte ich mit dem XMega als I2C-Master machen. Es sollen drei Register eines beliebigen Chips (hier eine DS1307) beschrieben und wieder ausgelesen werden. Das Schreiben, bzw. das Lesen soll sowohl mit, als auch ohne Interrupts erfolgen.

I2C-Master im normalen Modus:

Beginnen möchte ich mit der Realisierung eines I2C-Master ohne Interrupts. Die I2C-Schnittstelle der XMega-Familie ist, meiner Meinung nach, deutlich einfacher aufgebaut, als die der AVR8-Familie (wie z. B. beim Mega32). Intern arbeitet das I2C-Modul als Zustandsautomat und ist dank geschicktem Design mit sehr wenig Aufwand zu betreiben.

Das Modul ist zudem in ein Master- und ein Slave-Modul aufgeteilt, wodurch die einzelnen Betriebsmodi softwareseitig sehr gut voneinander getrennt werden können.

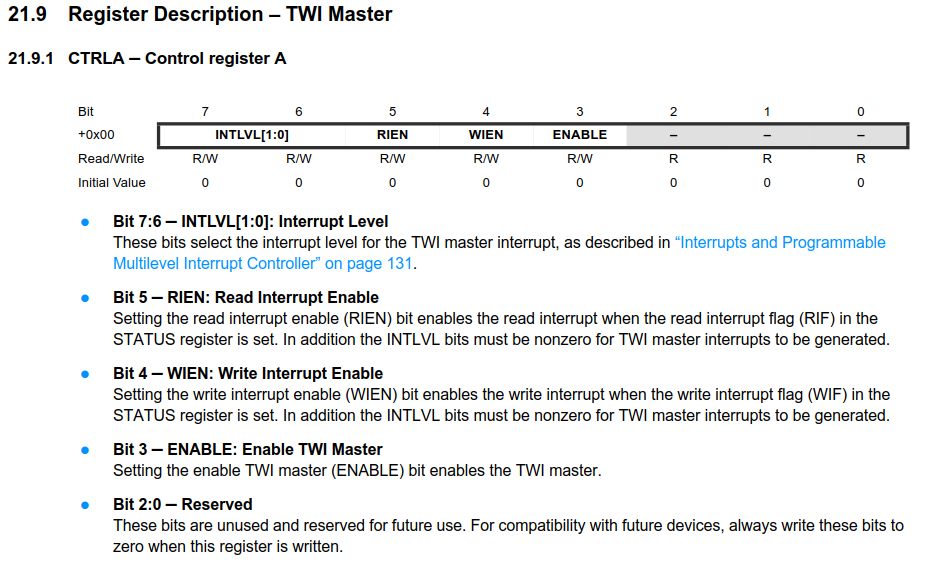

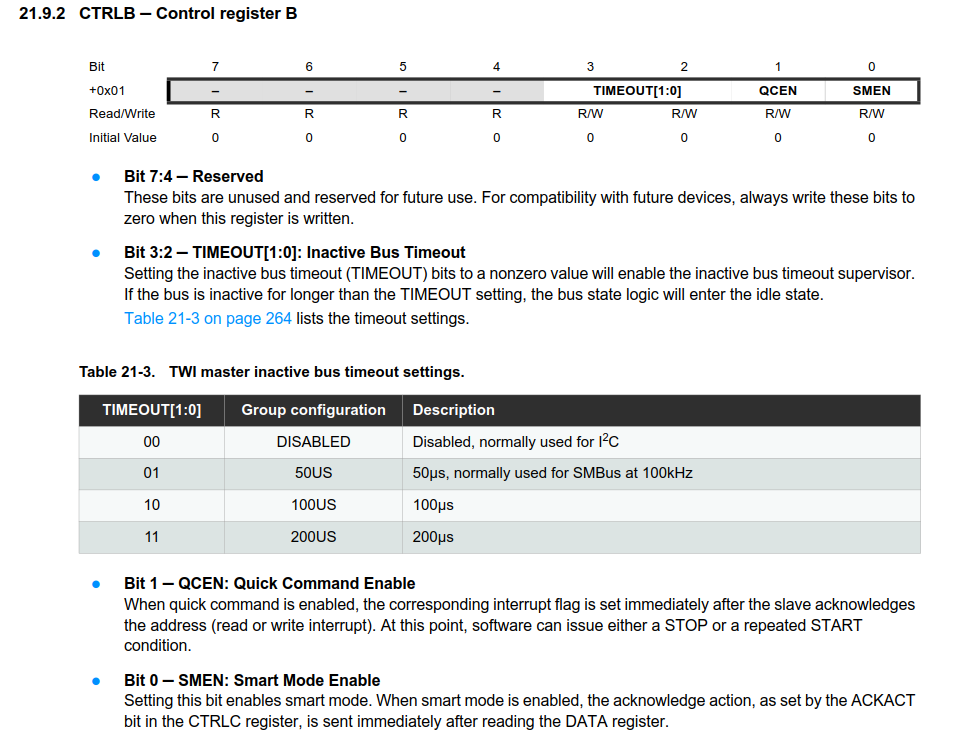

Die Konfiguration des Moduls erfolgt über das CTRLA– und das CTRLB-Register.

Über das BAUD-Register wird anschließend die Busfrequenz definiert. Die Busfrequenz muss sich dabei im Bereich zwischen 100 kHz und 400 kHz bewegen. Der Wert für das BAUD-Register lässt sich über die gegebene Formel berechnen:

![]()

Für eine Busfrequenz von 100 kHz bei 2 MHz Taktfrequenz ergibt sich ein Wert von 5 für das BAUD-Register.

TWIC.MASTER.BAUD = 0x05;

In diesem Beispiel werden keine Interrupts und keine zusätzlichen Modi genutzt, wodurch sich die Konfiguration auf die Aktivierung des Master-Modus reduziert:

TWIC.MASTER.CTRLA = TWI_MASTER_ENABLE_bm;

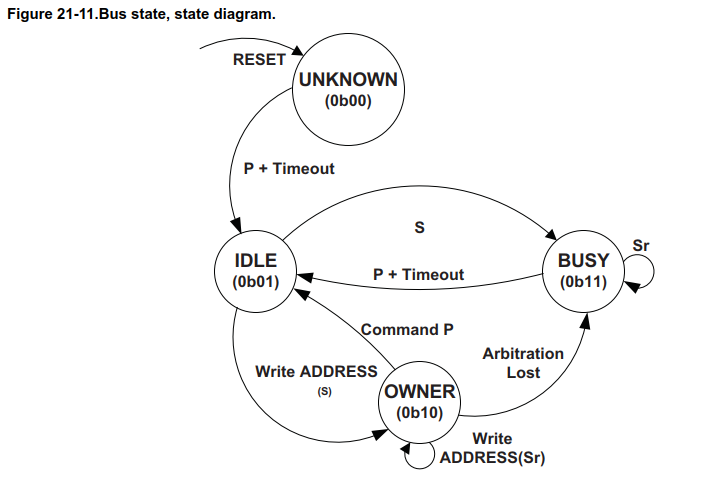

Nach einem Reset befindet sich das I2C-Modul im Zustand Unknown befindet und muss vor dem ersten Betrieb in den Zustand Idle gesetzt werden. Der aktuelle Zustand des Moduls ist über die ersten beiden Bits des STATUS-Registers einsehbar.

TWIC.MASTER.STATUS |= TWI_MASTER_BUSSTATE_IDLE_gc;

Hinweis:

Der Zustand des I2C-Moduls kann vom Anwender nicht geändert werden! Die einzige Ausnahme ist der Wechsel in den Idle-Modus!

Damit ist das I2C-Modul einsatzbereit. Zeit um die ersten Daten zu versenden…

Das Verhalten des Moduls wird über das ADDR-, das DATA– und das CTRLC-Register gesteuert. Sobald eine Adresse in das ADDR-Register geschrieben wird, erzeugt das I2C-Modul eine Startbedingung auf dem Bus und überträgt die Adresse. Für einen Schreibzugriff sieht das ganze dann folgendermaßen aus.

TWIC.MASTER.ADDR = 0x68 << 0x01;

Über das STATUS-Register kann dann überprüft werden ob das Addressbyte korrekt verwendet worden ist. Für einen Schreibzugriff muss das WIF-Bit und für einen Lesezugriff das RIF-Bit abgefragt werden.

// Schreibzugriff while(!((TWIC.MASTER.STATUS & TWI_MASTER_WIF_bm))); // Lesezugriff while(!((TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)));

Hinweis:

Da beide Bits beim Beschreiben des ADDR-Registers gelöscht werden, kann eine allgemeine Funktion zum Übertragen der Adresse gemacht werden, in der beide Bits abgefragt werden. Je nachdem welche Adresse in das ADDR-Register geschrieben und übertragen wird, wird entweder das WIF– oder das RIF-Bit gesetzt.

void TWIM_SendAddress(uint8_t Address)

{

TWIC.MASTER.ADDR = Address;

while(!((TWIC.MASTER.STATUS & TWI_MASTER_WIF_bm) || (TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)));

}

Jetzt können die Daten übertragen werden. Dazu werden die einzelnen Datenbytes nacheinander in das DATA-Register kopiert und darauf gewartet, dass das jeweilige Byte übertragen worden ist.

TWIC.MASTER.DATA = Data; while(!(TWIC.MASTER.STATUS & TWI_MASTER_WIF_bm));

Zum Abschluss muss eine Stop-Kondition erzeugt werden, indem das entsprechende Kommando in das CTRLC-Register geschrieben wird.

TWIC.MASTER.CTRLC = TWI_MASTER_CMD_STOP_gc;

Mit diesen paar Befehlen ist nun ein Byte per I2C übertragen worden. Schauen wir uns nun mal an, wie ein Datenbyte ausgelesen werden kann.

Damit ein Datenbyte ausgelesen werden kann, muss als erstes die entsprechende Leseadresse verschickt werden. Dies geschieht wieder über das ADDR-Register.

TWIC.MASTER.ADDR = (0x68 << 0x01) | 0x01;

Während der Übertragung der Adresse muss das RIF-Bit im STATUS-Register abgefragt werden um ein Übertragungsende zu erkennen.

while(!((TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)));

Über das RIF-Bit kann anschließend erkannt werden, wann ein neues Datenbyte empfangen worden ist. Dieses Datenbyte kann dann über das DATA-Register ausgelesen werden.

uint8_t Data = 0x00; while(!(TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)); Data = TWIC.MASTER.DATA;

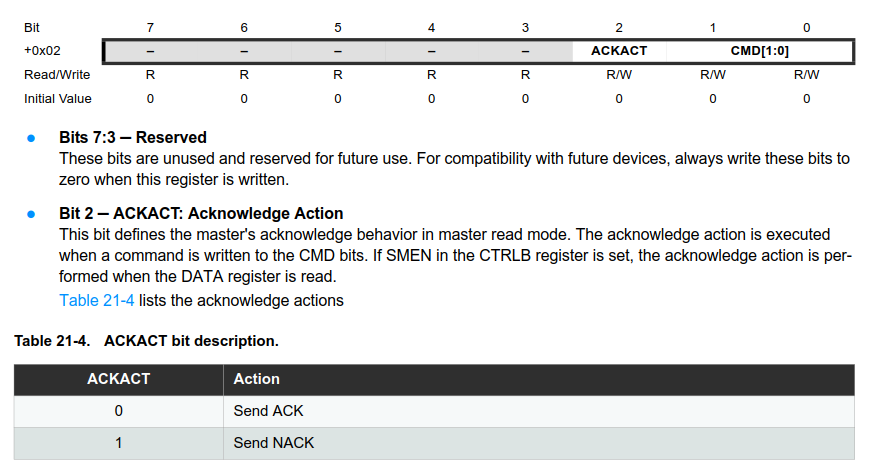

Der Empfang muss jetzt noch bestätigt werden, indem der Master ein ACK erzeugt. Dazu wird der entsprechende Befehl in das CTRLC-Register geschrieben.

TWIC.MASTER.CTRLC = TWI_MASTER_CMD_RECVTRANS_gc;

Falls es sich bei dem empfangenen Datenbyte um das letzte Datenbyte einer Übertragung handelt (z. B. weil der Puffer voll ist) muss der Master ein NACK erzeugen. Die Art der Bestätigung wird über das CTRLC-Register gesteuert.

Bei einem NACK wird zudem kein Bestätigungsbefehl in das CTRLC-Register geschrieben. Abgeschlossen wird die Übertragung mit einer Stop-Kondition und einem NACK.

TWIC.MASTER.CTRLC = TWI_MASTER_ACKACT_bm | TWI_MASTER_CMD_STOP_gc;

Für den Empfang ergibt sich damit der folgende Ablauf:

// Alle Datenbytes bis auf das letzte while(!(TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)); Data = TWIC.MASTER.DATA; TWIC.MASTER.CTRLC = TWI_MASTER_CMD_RECVTRANS_gc; // Empfangen des letzten Datenbytes while(!(TWIC.MASTER.STATUS & TWI_MASTER_RIF_bm)); Data = TWIC.MASTER.DATA; // Senden der Stop-Kondition TWIC.MASTER.CTRLC = TWI_MASTER_ACKACT_bm | TWI_MASTER_CMD_STOP_gc;

Damit ist der pollende Betrieb des I2C-Moduls auch schon abgeschlossen und das Modul einsatzbereit. Im nächsten Schritt zeige ich, wie man das Modul ausschließich über Interrupts nutzen kann.

I2C-Master im Interruptbetrieb:

Auch hier wird das Modul zuerst konfiguriert, wobei die Konfiguration vom ersten Beispiel übernommen und um das Setzen der Bits für die Interrupts erweitert werden kann:

TWIC.MASTER.BAUD = 0x05; TWIC.MASTER.CTRLA = TWI_MASTER_INTLVL_LO_gc | TWI_MASTER_RIEN_bm | TWI_MASTER_WIEN_bm | TWI_MASTER_ENABLE_bm; TWIC.MASTER.STATUS |= TWI_MASTER_BUSSTATE_IDLE_gc;

Für mein Beispiel verwende ich die Interruptpriorität Niedrig. Als nächstes müssen global die Interrupts aktiviert und die verwendeten Interruptprioritäten freigeschaltet werden.

PMIC.CTRL = PMIC_LOLVLEN_bm; sei();

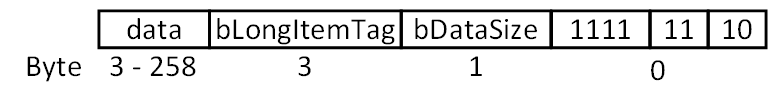

Für die Übertragung habe ich ein I2C-Nachrichtenobjekt erstellt, welches alle wichtigen Informationen beinhaltet:

typedef enum

{

TWI_MASTER_REGISTER = 0x00,

TWI_MASTER_ADDRESS = 0x01,

TWI_MASTER_WRITE = 0x02,

TWI_MASTER_READ = 0x03,

TWI_MASTER_SEND = 0x04,

TWI_MASTER_RECEIVED = 0x05,

TWI_MASTER_BUFFEROVERFLOW = 0x06,

TWI_MASTER_ERROR = 0xFF,

} TWI_MasterStatus_t;

typedef struct

{

TWI_t* Device;

uint8_t DeviceAddress;

uint8_t Register;

uint8_t BytesWrite;

uint8_t IndexWrite;

uint8_t BytesRead;

uint8_t IndexRead;

uint8_t* BufferWrite;

uint8_t* BufferRead;

TWI_MasterStatus_t Status;

} TWI_Message_t;

TWI_Message_t Message;

Das Objekt beinhaltet folgende Werte:

Die Einträge BytesRead, IndexRead und BufferRead werden später für den lesenden Zugriff verwendet. Der Eintrag Register beinhaltet die Adresse des ersten Registers auf dem I2C-Slave.

Eine Transaktion (wieder zuerst Schreiben) wird gestartet, indem das Nachrichtenobjekt mit Werten gefüllt und die Adresse des I2C-Slaves in das ADDR-Registers geschrieben wird.

uint8_t I2C_WriteBuffer[8];

for(uint8_t i = 0x00; i < 0x03; i++)

{

I2C_WriteBuffer[i] = i + 0x03;

}

Message.IndexWrite = 0x00;

Message.BufferWrite = I2C_WriteBuffer;

Message.BytesWrite = 0x03;

Message.Device = &TWIC;

Message.DeviceAddress = 0x68;

Message.Register = 0x00;

Message.Status = TWI_MASTER_REGISTER;

Message.Device->MASTER.ADDR = Message.DeviceAddress << 0x01;

Sobald die Startbedingung erzeugt und die Adresse übertragen worden ist, wird der entsprechende Interruptvektor für den Master-Interrupt vom genutzten TWI aufgerufen. In diesem wird als erstes das STATUS-Register ausgelesen, damit die Art des Interrupts bestimmt werden kann.

ISR(TWIC_TWIM_vect)

{

uint8_t Status = Message.Device->MASTER.STATUS;

}

Es können nun drei Fälle eintreten, die über die Statusbits dargestellt werden:

- Fehler bei der Übertragung – ARBLOST-Bit wird gesetzt

- Schreibzugriff auf den Slave – WIF-Bit wird gesetzt

- Lesezugriff auf den Slave – RIF-Bit wird gesetzt

ISR(TWIC_TWIM_vect)

{

uint8_t Status = Message.Device->MASTER.STATUS;

if(Status & TWI_MASTER_ARBLOST_bm)

{

TWIM_ArbitrationLostHandler();

}

else if(Status & TWI_MASTER_WIF_bm)

{

TWIM_WriteHandler();

}

}

Wenn das ARBLOST-Bit gesetzt ist, ist ein Übertragungsfehler aufgetreten. Die Übertragung wird somit direkt beendet und ein Fehlerzustand eingenommen.

void TWIM_ArbitrationLostHandler(void)

{

TWIM_ErrorHandler();

}

In diesem Fall wird das WIF-Bit gesetzt, da eine Schreibadresse übertragen und damit ein Schreibzugriff initiiert worden ist.

Die Funktion TWIM_WriteHandler implementiert einen Zustandsautomaten, der die Übertragung der Daten übernimmt. Dazu wird als erstes überprüft, ob der Slave ein NACK gesendet hat. Wenn ja, wird die Übertragung abgebrochen und ein Fehlerzustand eingenommen.

void TWIM_WriteHandler(void)

{

if(Message.Device->MASTER.STATUS & TWI_MASTER_RXACK_bm)

{

TWIM_ErrorHandler();

}

else

{

// Kein Fehler

}

}

Falls kein Fehler aufgetreten ist, wird der Zustandsautomat abgearbeitet. Als erstes wird geprüft ob sich der Automat im Zustand TWI_MASTER_REGISTER befindet. Wenn dies der Fall ist, soll als erstes eine Registeradresse übertragen werden. Dazu wird die Registeradresse in das DATA-Register des I2C-Moduls kopiert.

if(Message.Status == TWI_MASTER_REGISTER)

{

Message.Device->MASTER.DATA = Message.Register;

if(Message.BytesRead > 0x00)

{

Message.Status = TWI_MASTER_ADDRESS;

}

else

{

Message.Status = TWI_MASTER_WRITE;

}

}

Da es sich beim Versenden der Registeradresse immer um einen Schreibzugriff handelt, entfällt eine zusätzliche Acknowledge-Logik. Der nächste Zustand ist dann davon abhängig, ob es sich um einen schreibenden oder um einen lesenden Zugriff handeln soll. In diesem Fall ist es ersteres, weshalb der Zustand TWI_MASTER_WRITE eingenommen wird.

Sobald die Registeradresse übertragen worden ist, wird der Interruptvektor erneut aufgerufen und der Inhalt des STATUS-Registers ein weiteres mal überprüft. Das Programm springt erneut in die Funktion TWIM_WriteHandler und arbeitet den Zustandsautomaten weiter ab. In diesem Durchlauf wird der Zustand TWI_MASTER_WRITE bearbeitet:

else if(Message.Status == TWI_MASTER_WRITE)

{

if(Message.IndexWrite < Message.BytesWrite)

{

Message.Device->MASTER.DATA = Message.BufferWrite[Message.IndexWrite++];

}

else

{

Message.Device->MASTER.CTRLC = TWI_MASTER_CMD_STOP_gc;

Message.Status = TWI_MASTER_SEND;

}

}

In diesem Zustand werden die einzelnen Datenbytes versendet und der Indexzeiger inkrementiert. Wenn alle Daten versendet worden sind, wird eine Stop-Kondition ausgelöst und der Zustand auf TWI_MASTER_SEND geändert. Damit ist die Übertragung abgeschlossen.

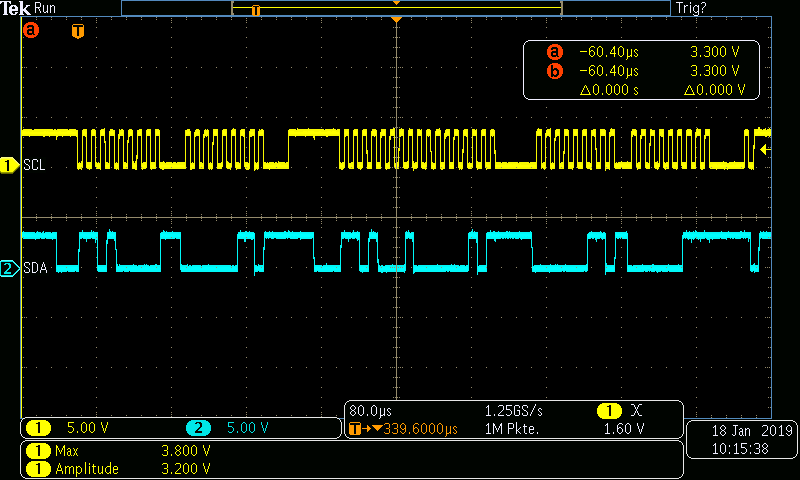

Der lesende Zugriff läuft ähnlich ab. Zuerst wird das I2C-Nachrichtenobjekt wieder mit Werten gefüllt:

uint8_t I2C_ReadBuffer[8]; Message.IndexRead = 0x00; Message.BufferRead = I2C_ReadBuffer; Message.BytesRead = 0x03; Message.Device = &TWIC; Message.DeviceAddress = 0x68; Message.Register = 0x00; Message.Status = TWI_MASTER_REGISTER; Message.Device->MASTER.ADDR = Message.DeviceAddress << 0x01;

Wichtig ist hier, dass zuerst die Schreibadresse in das ADDR-Registers geschrieben wird, da der Adresszeiger des I2C-Slaves noch gesetzt werden muss. Falls nur gelesen werden soll, ohne das der Adresszeiger geändert wird, werden folgen Werte verwendet:

Message.IndexRead = 0x00; Message.BufferRead = I2C_ReadBuffer; Message.BytesRead = 0x03; Message.Device = &TWIC; Message.DeviceAddress = 0x68; Message.Register = 0x00; Message.Status = TWI_MASTER_READ; Message.Device->MASTER.ADDR = (Message.DeviceAddress << 0x01) | 0x01;

Durch das Beschreiben des ADDR-Registers wird dann wieder die Übertragung gestartet. Falls eine Registeradresse übertragen werden soll, geschieht dies analog zum schreibenden Zugriff, außer das nach dem Senden der Registeradresse der Zustand TWI_MASTER_ADDRESS eingenommen wird, damit nach dem Senden der Registeradresse eine weitere Start-Kondition mit der Adresse für einen lesenden Zugriff gesendet wird.

if(Message.Status == TWI_MASTER_REGISTER)

{

Message.Device->MASTER.DATA = Message.Register;

if(Message.BytesRead > 0x00)

{

Message.Status = TWI_MASTER_ADDRESS;

}

else

{

Message.Status = TWI_MASTER_WRITE;

}

}

else if(Message.Status == TWI_MASTER_ADDRESS)

{

Message.Device->MASTER.ADDR = TWI_READ(Message.DeviceAddress);

Message.Status = TWI_MASTER_READ;

}

Sobald die Leseadresse versendet worden ist, springt das I2C-Modul erneut in den Interruptvektor. Dieses mal wird allerdings das RIF-Bit gesetzt und die Funktion TWIM_ReadHandler aufgerufen:

ISR(TWIC_TWIM_vect)

{

uint8_t Status = Message.Device->MASTER.STATUS;

if(Status & TWI_MASTER_ARBLOST_bm)

{

TWIM_ArbitrationLostHandler();

}

else if(Status & TWI_MASTER_WIF_bm)

{

TWIM_WriteHandler();

}

else if(Status & TWI_MASTER_RIF_bm)

{

TWIM_ReadHandler();

}

}

Die Funktion TWIM_ReadHandler liest nun die einzelnen Datenbytes aus und erzeugt die entsprechende Bestätigung für den I2C-Slave.

if(Message.IndexRead < TWI_BUFFER_SIZE)

{

Message.BufferRead[Message.IndexRead++] = Message.Device->MASTER.DATA;

}

else

{

Message.Device->MASTER.CTRLC = TWI_MASTER_ACKACT_bm | TWI_MASTER_CMD_STOP_gc;

Message.Status = TWI_MASTER_BUFFEROVERFLOW;

}

if(Message.IndexRead < Message.BytesRead)

{

Message.Device->MASTER.CTRLC = TWI_MASTER_CMD_RECVTRANS_gc;

}

else

{

Message.Device->MASTER.CTRLC = TWI_MASTER_ACKACT_bm | TWI_MASTER_CMD_STOP_gc;

Message.Status = TWI_MASTER_RECEIVED;

}

Als erstes wird geprüft ob der aktuelle Leseindex größer ist als die Länge des Lesepuffers. Wenn dies der Fall ist, wird ein NACK mit einer Stop-Kondition gesendet und der Master in einen Fehlerzustand versetzt. Andernfalls wird das aktuelle Datenbyte aus dem DATA-Register ausgelesen, gespeichert und der Index inkrementiert. Der Empfang wird mit einem ACK quittiert. Sobald alle Daten empfangen worden sind, wird statt dem ACK ein NACK und eine Stop-Kondition gesendet und der Zustand TWI_MASTER_RECEIVED eingenommen. Damit ist die Übertragung abgeschlossen.

XMega als I2C-Slave:

Da der Master-Modus nun komplett ist, wollen wir uns mit dem Slave-Modus beschäftigen. Dieser Modus kann ebenfalls mit und ohne Interrupts realisiert werden. Da ich aber eine Realisierung ohne Interrupts für unnötig halte – warum sollte der Mikrocontroller so lange nichts tun, bis Daten an ihn gesendet werden? – zeige ich hier lediglich eine Implementierung des I2C-Slave über Interrupts. Das Prinzip kann dann, falls Bedarf besteht, auf eine Realisierung ohne Interrupts übertragen werden.

Für das Beispiel als I2C-Slave nutze ich beide I2C-Module des XMega, wobei das Modul TWIC als I2C-Master und das Modul TWIE als I2C-Slave konfiguriert wird.

TWIC.MASTER.BAUD = 0x05; TWIC.MASTER.CTRLA = TWI_MASTER_INTLVL_LO_gc | TWI_MASTER_RIEN_bm | TWI_MASTER_WIEN_bm | TWI_MASTER_ENABLE_bm; TWIC.MASTER.STATUS |= TWI_MASTER_BUSSTATE_IDLE_gc; TWIE.SLAVE.CTRLA = TWI_SLAVE_INTLVL_LO_gc | TWI_SLAVE_DIEN_bm | TWI_SLAVE_APIEN_bm | TWI_SLAVE_PIEN_bm | TWI_SLAVE_ENABLE_bm; TWIE.SLAVE.ADDR = (0x40 << 0x01); TWIE.SLAVE.ADDRMASK = 0x00;

Beide Module werden ausschließlich über Interrupts gesteuert und die Adresse des Slave-Moduls soll 0x40 lauten. Diese Adresse muss in das ADDR-Register des Slave-Moduls geschrieben werden. Über das ADDRMASK-Register können bestimmte Bits bei einem Vergleich der Adresse ausgeschaltet werden, sodass das Modul z. B. auf einen bestimmten Adressbereich reagiert. Diese Funktion soll hier nicht genutzt werden, weshalb das Register geleert wird.

Damit ist die Konfiguration des Slave-Moduls abgeschlossen. Auch für das Slave-Modul habe ich eine Verarbeitung mittels Zustandsautomaten realisiert und in einem entsprechenden Objekt hinterlegt:

typedef enum

{

TWI_SLAVE_IDLE = 0x00,

TWI_SLAVE_BUFFEROVERFLOW = 0x01,

TWI_SLAVE_ERROR = 0xFF,

} TWI_SlaveStatus_t;

typedef struct

{

TWI_t* Device;

uint8_t* Buffer;

uint8_t BytesReceived;

uint8_t BytesSend;

uint8_t WriteIndex;

uint8_t ReadIndex;

TWI_SlaveStatus_t Status;

} TWI_Buffer_t;

TWI_Buffer_t SlaveBuffer;

Dieses Objekt wird vor der ersten Nutzung initialisiert:

uint8_t I2C_SlaveBuffer[8]; SlaveBuffer.Buffer = I2C_SlaveBuffer; SlaveBuffer.Device = &TWIE; SlaveBuffer.BytesReceived = 0x00; SlaveBuffer.BytesSend = 0x00; SlaveBuffer.WriteIndex = 0x00; SlaveBuffer.ReadIndex = 0x00; SlaveBuffer.Status = TWI_SLAVE_IDLE;

Sobald etwas auf dem Bus passiert wird der entsprechende Interruptvektor für den I2C-Slave aufgerufen. Auch hier wird zuerst das STATUS-Register des I2C-Moduls ausgelesen.

ISR(TWIE_TWIS_vect)

{

uint8_t Status = SlaveBuffer.Device->SLAVE.STATUS;

if(Status & TWI_SLAVE_BUSERR_bm)

{

TWIS_ErrorHandler();

}

else if(Status & TWI_SLAVE_COLL_bm)

{

TWIS_ErrorHandler();

}

else if((Status & TWI_SLAVE_APIF_bm) && (Status & TWI_SLAVE_AP_bm))

{

TWIS_AddressMatchHandler();

}

else if(Status & TWI_SLAVE_APIF_bm)

{

TWIS_StopHandler();

}

else if(Status & TWI_SLAVE_DIF_bm)

{

TWIS_DataHandler();

}

else

{

TWIS_ErrorHandler();

}

}

Für den Fall das ein Fehler auf dem I2C-Bus, eine Kollision oder sonstige Zustände auftreten wird ein Fehlerzustand eingenommen.

Wenn das APIF-Bit und das AP-Bit gesetzt sind, hat das Slave-Modul eine gültige Adresse empfangen. In diesem Fall wird der TWIS_AddressMatchHandler abgearbeitet, in dem die Zähler für die empfangenen und übertragenden Bytes auf null gesetzt und die Anfrage für den Master quittiert wird.

void TWIS_AddressMatchHandler(void)

{

SlaveBuffer.BytesReceived = 0x00;

SlaveBuffer.BytesSend = 0x00;

SlaveBuffer.Device->SLAVE.CTRLB = TWI_SLAVE_CMD_RESPONSE_gc;

}

Sobald die Adresse des Masters bestätigt worden ist, beginnt der Master mit dem Transfer der Daten. Bei jedem Datenbyte wird das DIF-Flag im STATUS-Register gesetzt und der TWIS_DataHandler aufgerufen.

void TWIS_DataHandler(void)

{

uint8_t Status = SlaveBuffer.Device->SLAVE.STATUS;

if(Status & TWI_SLAVE_DIR_bm)

{

if(SlaveBuffer.Device->SLAVE.STATUS & TWI_SLAVE_RXACK_bm)

{

SlaveBuffer.Device->SLAVE.CTRLB = TWI_SLAVE_CMD_COMPTRANS_gc;

}

else

{

SlaveBuffer.BytesSend++;

SlaveBuffer.Device->SLAVE.DATA = SlaveBuffer.Buffer[SlaveBuffer.ReadIndex++];

if(SlaveBuffer.ReadIndex > TWI_BUFFER_SIZE)

{

SlaveBuffer.ReadIndex = 0x00;

SlaveBuffer.Status = TWI_SLAVE_BUFFEROVERFLOW;

}

SlaveBuffer.Device->SLAVE.CTRLB = TWI_SLAVE_CMD_RESPONSE_gc;

}

}

else

{

SlaveBuffer.BytesReceived++;

SlaveBuffer.Buffer[SlaveBuffer.WriteIndex++] = SlaveBuffer.Device->SLAVE.DATA;

if(SlaveBuffer.WriteIndex > TWI_BUFFER_SIZE)

{

SlaveBuffer.Device->SLAVE.CTRLB = TWI_SLAVE_ACKACT_bm;

SlaveBuffer.Status = TWI_SLAVE_BUFFEROVERFLOW;

}

SlaveBuffer.Device->SLAVE.CTRLB |= TWI_SLAVE_CMD_RESPONSE_gc;

}

}

Diese Funktion ließt das STATUS-Register aus und bestimmt anhand des DIR-Bits ob es sich, seitens des Masters, um einen schreibenden oder einen lesenden Zugriff handelt. Wenn es sich um einen schreibenden Zugriff handelt, ist das Bit nicht gesetzt. Dann werden die empfangenen Bytes in den Datenpuffer vom Slave-Modul geschrieben und der entsprechende Empfangszähler erhöht.

Jedes empfangene Datenbyte wird durch ein Response-Kommando mit einem ACK bestätigt. Falls der Master zu viele Daten sendet und dadurch ein Pufferüberlauf entsteht, wird ein NACK gesendet, sodass der Master die Kommunikation beendet. Zudem wird ein entsprechender Fehlerstatus eingenommen.

Wenn es sich um einen lesenden Zugriff handelt (DIR = 1), werden die einzelnen Datenbytes aus dem Puffer in das DATA-Register des Moduls kopiert und versendet. Falls der Master mit einem NACK bestätigt hat (RXACK = 1) wird die Übertragung beendet. Auch hier wird wieder ein entsprechender Fehler ausgelöst, wenn es zu einem Pufferüberlauf kommt.

Sobald alle Daten vom Master gesendet, bzw. empfangen worden sind (oder es zu einem Fehler kommt), sendet dieser eine Stop-Kondition. In diesem Fall wird der TWIS_StopHandler aufgerufen, der in diesem Fall nur das entsprechende Interruptbit löscht:

void TWIS_StopHandler(void)

{

SlaveBuffer.Device->SLAVE.STATUS |= TWI_SLAVE_APIF_bm;

}

Damit ist der I2C-Slave komplett implementiert und einsatzbereit. Das Programm kann sehr bequem mit einem XMega mit zwei I2C-Modulen getestet werden, da man lediglich eine Brücke zwischen SDA und SCL beider Module bilden muss (Pull-Up Widerstände nicht vergessen!).

Das komplette Projekt inkl. mehrerer Beispielanwendungen für den Master- und den Slave-Betrieb steht in meinem GitHub-Repository zum Download bereit.

Hey, i always got an error becouse : The BAUD register should be written only while the master is disabled. So it is important to change the order of the initialisation.

Greetings Jan