In diesem Teil des I2S Tutorials für FPGAs möchte ich zeigen, wie der bereits erstellte I2S-Sender mit einem AXI-Stream Interface ausgestattet werden kann, wodurch es möglich ist den I2S-Sender über einen AXI-Stream FIFO mit dem Processing System zu verbinden.

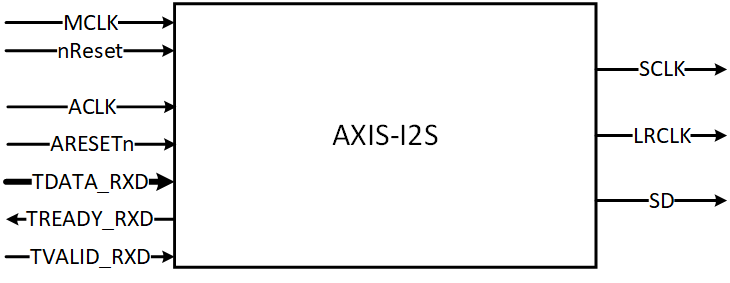

Dazu wird ein neues Top-Design namens AXIS_I2S angelegt. Dieses Design soll über folgende I/O verfügen:

Die dazu gehörige Entität sieht folgendermaßen aus:

entity AXIS_I2S is

Generic ( RATIO : INTEGER := 8;

WIDTH : INTEGER := 16

);

Port ( MCLK : in STD_LOGIC;

nReset : in STD_LOGIC;

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC;

ACLK : in STD_LOGIC;

ARESETn : in STD_LOGIC;

TDATA_RXD : in STD_LOGIC_VECTOR(31 downto 0);

TREADY_RXD : out STD_LOGIC;

TVALID_RXD : in STD_LOGIC

);

end AXIS_I2S;

Über den Parameter RATIO wird das Verhältnis von SCLK zu MCKL und über den Parameter WIDTH die Breite eines Datenwortes pro Kanal definiert.

Hinweis:

Die hier vorgestellte Implementierung unterstützt lediglich 16 Bit Datenwörter pro Kanal (also 32 Bit für Stereo). Für höhere Busbreiten muss der nachfolgende Code angepasst werden.

In dem Design müssen folgende Komponenten implementiert werden:

- Ein Teiler um aus MCLK den Eingangstakt für den I2S-Sender zu generieren

- Ein AXI-Stream Slave Interface

- Die Steuerung des I2S-Senders

Für den Teiler wird ein Prozess erstellt, der bei der steigenden Taktflanke von MCLK einen Zähler hochzählt und nach der halben Periode das Signal SCLK_Int umschaltet.

process

variable Counter : INTEGER := 0;

begin

wait until rising_edge(MCLK);

if(Counter < ((RATIO / 2) - 1)) then

Counter := Counter + 1;

else

Counter := 0;

SCLK_Int <= not SCLK_Int;

end if;

if(nReset = '0') then

Counter := 0;

SCLK_Int <= '0';

end if;

end process;

Als nächstes wird das AXI-Stream Interface implementiert. Dazu wird ein Zustandsautomat genutzt:

AXIS_Proc : process

begin

wait until rising_edge(ACLK);

case CurrentState is

when STATE_WAIT_TRANSMITTER_READY =>

if((Ready_Fast = '1') and (src_rcv = '0')) then

CurrentState <= STATE_WAIT_VALID;

else

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

end if;

when STATE_WAIT_VALID =>

if(AXIS_TransferDone = '1') then

Data_Fast <= TDATA_RXD;

src_send <= '1';

CurrentState <= STATE_WAIT_TRANSMITTER_BUSY;

else

CurrentState <= STATE_WAIT_VALID;

end if;

when STATE_WAIT_TRANSMITTER_BUSY =>

if((Ready_Fast = '0') and (src_rcv = '1')) then

src_send <= '0';

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

else

CurrentState <= STATE_WAIT_TRANSMITTER_BUSY;

end if;

end case;

if(ARESETn = '0') then

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

end if;

end process;

Nach einem Reset wechselt der Automat vom Reset-Zustand in den Zustand STATE_WAIT_TRANSMITTER_READY, wo er auf das Ready-Signal des I2S-Senders wartet. Sobald der Sender bereit ist, wird das Signal TREADY_RXD des AXI-Stream Interfaces gesetzt, wodurch der Master darüber informiert wird, dass der Slave bereit ist Daten zu empfangen. Anschließend wechselt der Slave in den Zustand STATE_WAIT_VALID.

In diesem Zustand wartet der Slave darauf das der Master das Signal TVALID_RXD setzt um gültige Daten zu markieren. Sobald das Signal gesetzt wird, werden die Daten in einen internen FIFO geschrieben. Der Automat wechselt dann in den Zustand STATE_WAIT_TRANSMITTER_BUSY.

Jetzt wartet der Zustandsautomat darauf, dass der I2S-Sender mit der Übertragung der Daten beginnt und das Ready-Signal löscht. Sobald dies geschehen ist, wechselt der Automat zurück in den Zustand STATE_WAIT_TRANSMITTER_READY und wartet wieder so lange bis der I2S-Sender bereit ist.

Damit wäre das AXI-Stream Interface in der Theorie fertig. Leider wird es zum Schluss noch etwas kniffelig, da der aktuelle Schaltungsentwurf zwei verschiedene Taktdomainen verwendet:

- Die Domain von ACLK, also dem Taktsignal des AXI-Stream Interfaces

- Die Domain von MCLK, also dem Taktsignal des Audio Interfaces

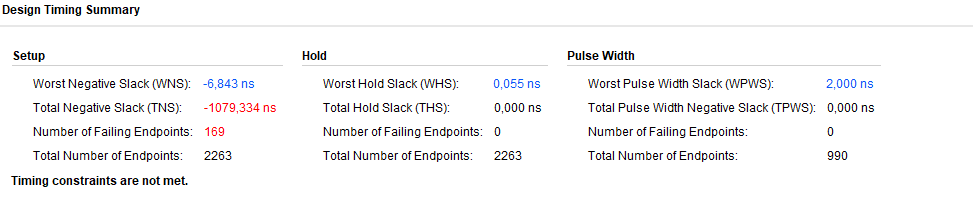

In der Regel können diese beiden Taktsignale nicht aus einer Taktquelle generiert werden (z. B. über einen Taktteiler), da das AXI-Interface auf typischerweise 100 MHz läuft und das Audio Interface Taktraten benötigt, die sich sauber auf die Abtastfrequenz runterteilen lassen, wie z. B. 12,288 MHz. Dies hat zur Folge, dass bei der Implementierung Timing Fehler auf Grund eines zu hohen Worst Negative Slack (WNS) und Total Negative Slack (TNS) auftreten:

Zudem ist das Risiko von fehlerhaften Daten durch eine auftretende Metastabilität der Flipflops bei unterschiedlichen Taktdomainen sehr hoch. Metastabilität tritt u. a. dann auf, wenn ein Flipflop schaltet und sich die Daten genau in dem Moment ändern.

Daher müssen die Signale, die von den einzelnen Taktdomainen genutzt werden, über entsprechende Schaltungen in die jeweils andere Taktdomain überführt werden. Xilinx beschreibt in dem Dokument UG953 entsprechende Makros, die für diesen Zweck genutzt werden können.

Für den vorliegenden VHDL-Code können die Beispiele der Makros direkt übernommen werden:

xpm_cdc_Data : xpm_cdc_handshake generic map ( DEST_EXT_HSK => 0,

DEST_SYNC_FF => 4,

INIT_SYNC_FF => 0,

SIM_ASSERT_CHK => 0,

SRC_SYNC_FF => 4,

WIDTH => (2 * WIDTH)

)

port map ( src_clk => ACLK,

src_in => Data_Fast,

dest_clk => MCLK,

dest_out => Data_Slow,

dest_ack => '0',

src_send => src_send,

src_rcv => src_rcv,

dest_req => dest_req

);

xpm_cdc_Ready : xpm_cdc_single generic map ( DEST_SYNC_FF => 4,

SRC_INPUT_REG => 1

)

port map ( src_clk => MCLK,

src_in => Ready_Slow,

dest_clk => ACLK,

dest_out => Ready_Fast

);

Zum Schluss muss noch der I2S-Sender eingefügt und die erzeugten Signale weitergegeben werden.

Transmitter : I2S_Transmitter generic map ( WIDTH => WIDTH

)

port map( Clock => SCLK_Int,

nReset => nReset,

Ready => Ready_Slow,

Tx => Data_Slow,

LRCLK => LRCLK,

SCLK => SCLK,

SD => SD

);

Damit ist das AXI-Stream Interface für den I2S-Sender ist damit fertig und einsatzbereit. Der komplette Code sollte nun wie folgt aussehen:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library xpm;

use xpm.vcomponents.all;

entity AXIS_I2S is

Generic ( RATIO : INTEGER := 8;

WIDTH : INTEGER := 16

);

Port ( MCLK : in STD_LOGIC;

nReset : in STD_LOGIC;

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC;

ACLK : in STD_LOGIC;

ARESETn : in STD_LOGIC;

TDATA_RXD : in STD_LOGIC_VECTOR(31 downto 0);

TREADY_RXD : out STD_LOGIC;

TVALID_RXD : in STD_LOGIC

);

end AXIS_I2S;

architecture AXIS_I2S_Arch of AXIS_I2S is

type AXIS_State_t is (STATE_WAIT_TRANSMITTER_READY, STATE_WAIT_VALID, STATE_WAIT_TRANSMITTER_BUSY);

signal CurrentState : AXIS_State_t := STATE_WAIT_TRANSMITTER_READY;

signal Data_Fast : STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0) := (others => '0');

signal Data_Slow : STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0) := (others => '0');

signal Ready_Fast : STD_LOGIC;

signal Ready_Slow : STD_LOGIC;

signal SCLK_Int : STD_LOGIC := '0';

signal AXIS_TransferDone : STD_LOGIC := '0';

signal AXIS_TREADY : STD_LOGIC := '0';

signal src_send : STD_LOGIC := '0';

signal src_rcv : STD_LOGIC := '0';

signal dest_req : STD_LOGIC := '0';

component I2S_Transmitter is

Generic ( WIDTH : INTEGER := 16

);

Port ( Clock : in STD_LOGIC;

nReset : in STD_LOGIC;

Ready : out STD_LOGIC;

Tx : in STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0);

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC

);

end component;

begin

Transmitter : I2S_Transmitter generic map ( WIDTH => WIDTH

)

port map( Clock => SCLK_Int,

nReset => nReset,

Ready => Ready_Slow,

Tx => Data_Slow,

LRCLK => LRCLK,

SCLK => SCLK,

SD => SD

);

xpm_cdc_Data : xpm_cdc_handshake generic map ( DEST_EXT_HSK => 0,

DEST_SYNC_FF => 4,

INIT_SYNC_FF => 0,

SIM_ASSERT_CHK => 0,

SRC_SYNC_FF => 4,

WIDTH => (2 * WIDTH)

)

port map ( src_clk => ACLK,

src_in => Data_Fast,

dest_clk => MCLK,

dest_out => Data_Slow,

dest_ack => '0',

src_send => src_send,

src_rcv => src_rcv,

dest_req => dest_req

);

xpm_cdc_Ready : xpm_cdc_single generic map ( DEST_SYNC_FF => 4,

SRC_INPUT_REG => 1

)

port map ( src_clk => MCLK,

src_in => Ready_Slow,

dest_clk => ACLK,

dest_out => Ready_Fast

);

GenSCLK_Proc : process

variable Counter : INTEGER := 0;

begin

wait until rising_edge(MCLK);

if(Counter < ((RATIO / 2) - 1)) then

Counter := Counter + 1;

else

Counter := 0;

SCLK_Int <= not SCLK_Int;

end if;

if(nReset = '0') then

Counter := 0;

SCLK_Int <= '0';

end if;

end process;

AXIS_TREADY <= '1' when (CurrentState = STATE_WAIT_VALID) else '0';

AXIS_TransferDone <= '1' when ((AXIS_TREADY = '1') and (TVALID_RXD = '1')) else '0';

AXIS_Proc : process

begin

wait until rising_edge(ACLK);

case CurrentState is

when STATE_WAIT_TRANSMITTER_READY =>

if((Ready_Fast = '1') and (src_rcv = '0')) then

CurrentState <= STATE_WAIT_VALID;

else

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

end if;

when STATE_WAIT_VALID =>

if(AXIS_TransferDone = '1') then

Data_Fast <= TDATA_RXD;

src_send <= '1';

CurrentState <= STATE_WAIT_TRANSMITTER_BUSY;

else

CurrentState <= STATE_WAIT_VALID;

end if;

when STATE_WAIT_TRANSMITTER_BUSY =>

if((Ready_Fast = '0') and (src_rcv = '1')) then

src_send <= '0';

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

else

CurrentState <= STATE_WAIT_TRANSMITTER_BUSY;

end if;

end case;

if(ARESETn = '0') then

CurrentState <= STATE_WAIT_TRANSMITTER_READY;

end if;

end process;

TREADY_RXD <= AXIS_TREADY;

end AXIS_I2S_Arch;

Der erstellte AXI-Stream I2S-Sender kann jetzt noch bei Bedarf als IP-Core für Vivado erstellt werden, wobei ich die notwendigen Schritte hier auslassen werde. Alternativ kann der fertige IP-Core auch aus dem GitHub-Repository des Projektes heruntergeladen werden.

→ Zurück

Hallo,

ich dachte der Synchronizer mit Gray Code ist nur anwendbar wenn auf/absteigende Werte (wie Adressen) übertragen werden.

Ansonsten ändert sich mehr als ein Bit und man hat wieder die Probleme mit Metastabilität. Wenn sich nur ein Bit ändert, dann hat man am Ausgang entweder den alten oder den neuen Wert (und nichts dazwischen).

Also wenn man erst 00 und dann 01 überträgt kann man 00 oder 01 am anderen Ende beobachten. Wenn man 00 und dann 11 überträgt kann man im anderen Domain zwischenzeitlich 00, 01, 10 oder 11 sehen bevor es sich auf 11 stabilisiert.

Hallo Martin,

stimmt. Da habe ich wohl nicht sauber gelesen. Ich habe den Code entsprechend angepasst.

Gruß

Daniel