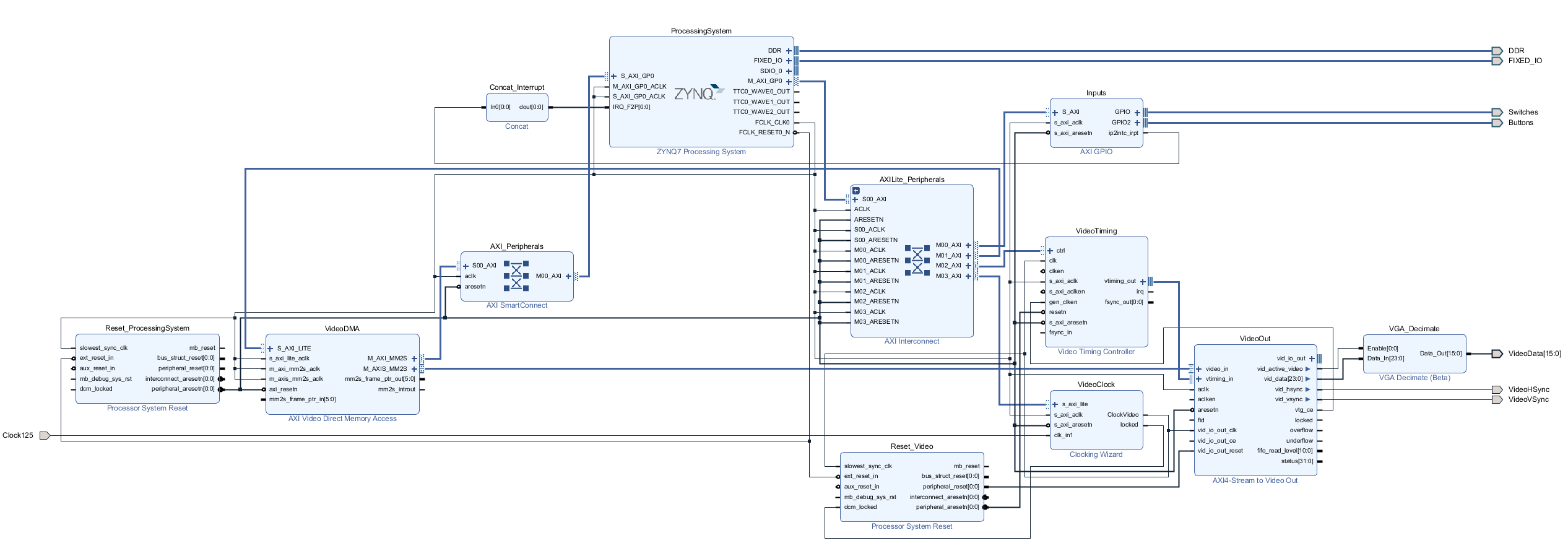

Die benötigte Hardware und deren Konfiguration ist relativ umfangreich. Um die Komplexität und die Länge möglichst gering zu halten, werde ich für die Hardware und die Software verschiedene Kapitel erstellen. Beginnen möchte ich mit der genutzten Hardware.

Für die Ausgabe eines Videosignals werden die folgenden Komponenten benötigt:

- Processing System

- AXI Video DMA

- Video Timing Controller

- Clocking Wizard

- Video Timing Controller

- AXI4-Stream to Video Out

- AXI GPIO

- VGA Decimate IP-Core aus dem Projektverzeichnis

Konfiguration des Processing Systems:

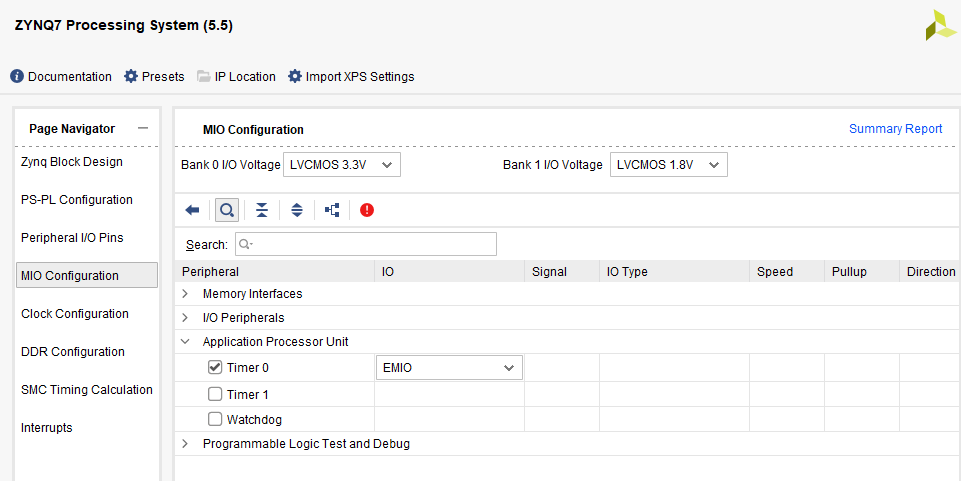

Das Processing System übernimmt die Steuerung des Designs. Hierfür wird die Standardkonfiguration aus dem Git-Repository verwendet. Diese Konfiguration wird zusätzlich um den Timer 0 als Zeitgeber, ein GP Slave AXI Interface und den PL-PS Interrupt Port erweitert.

- MIO Configuration → Application Processor Unit → Timer 0

- PS-PL Configuration → GP Slave AXI Interface → S AXI GP0 Interface

- Interrupts → Fabric Interrupts → PL-PS Interrupt Port → IRQ_F2P[15:0]

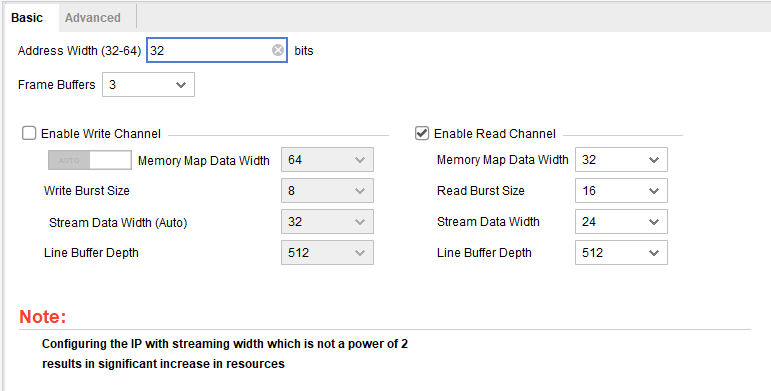

Konfiguration des Video DMA:

Der Video DMA übernimmt den Datentransfer vom Display-RAM, welcher sich im DDR-RAM des Prozessors befindet, zum VGA-Interface. Die Parametrierung des DMA findet über ein AXI4-Lite Interface statt und für den Datentransfer stehen zwei AXI-Interfaces zur Verfügung

- MM2S (Memory Mapped to Slave) – Lesekanal

- S2MM (Slave to Memory Mapped) – Schreibkanal

In diesem Beispiel kann der Schreibkanal deaktiviert werden, da nur Bilder aus dem Speicher gelesen werden sollen.

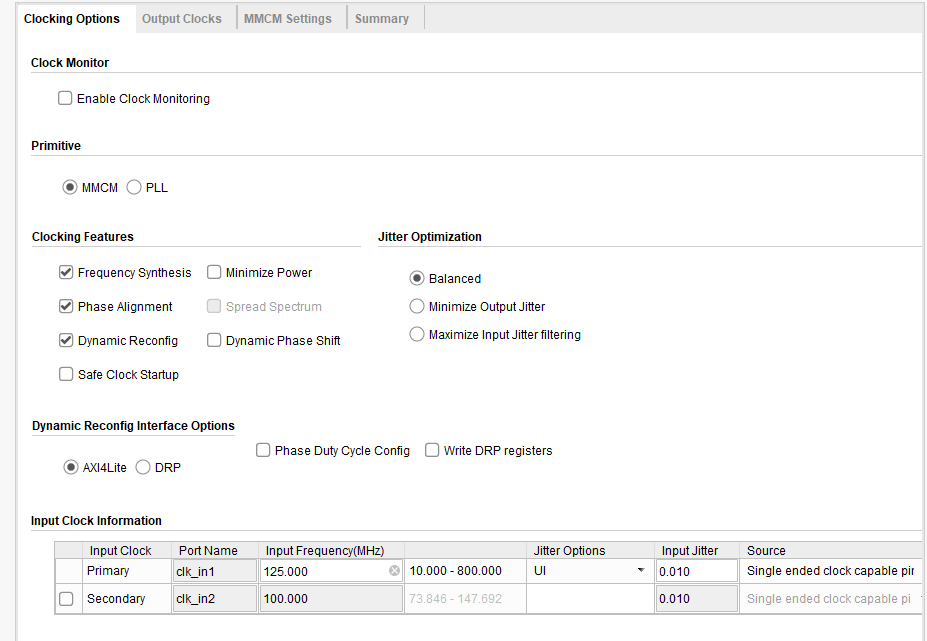

Konfiguration des Clocking Wizard:

Der Clocking Wizard hat die Aufgabe den Basistakt für das Videosignal zu produzieren. Damit die Auflösung umgestellt werden kann, muss der Clocking Wizard zudem mit einem AXI4-Lite Interface ausgestattet werden.

Über das Konfigurationsmenü des Clocking Wizards kann man leicht die Parameter für eine bestimmte Zielfrequenz bestimmen. Es ist daher sinnvoll das Menü zu nutzen um die Parameter für die verschiedenen Bildfrequenzen zu bestimmen:

- 25,175 MHz für 640×480 Pixel

- 40 MHz für 800×600 Pixel

- 65 MHz für 1024×768 Pixel

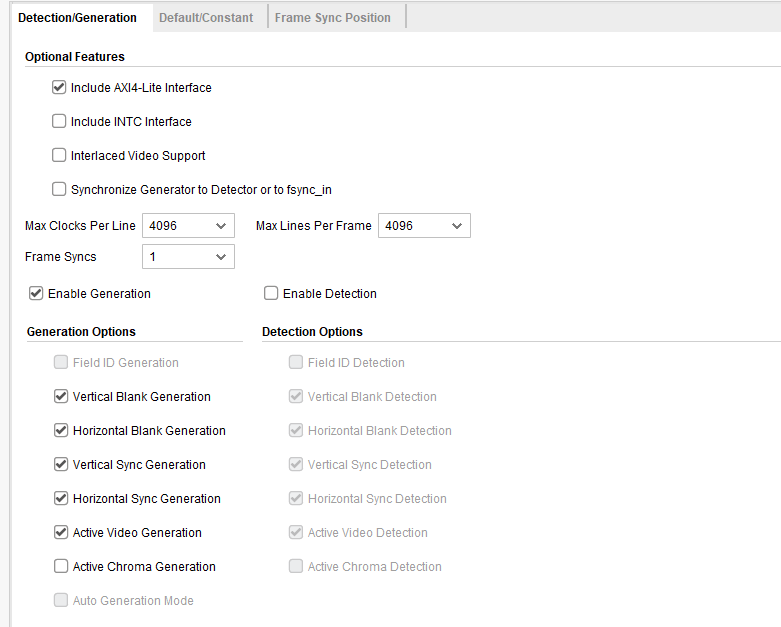

Konfiguration des Video Timing Controllers:

Der Video Timing Controller generiert aus dem Basistakt für das Videosignal die notwendigen Steuersignale für den Bildschirm, verschiedene Synchronisationssignale und ein Enable-Signal für die einzelnen Pixel. Auch dieser IP-Core benötigt ein AXI4-Lite Interface, damit die Bildschirmauflösung angepasst werden kann. Der IP-Core besitzt zudem die Möglichkeit Bildsignale, wie z. B. ein HSync-Signal, zu erkennen. Diese Funktion wird in diesem Beispiel jedoch nicht benötigt.

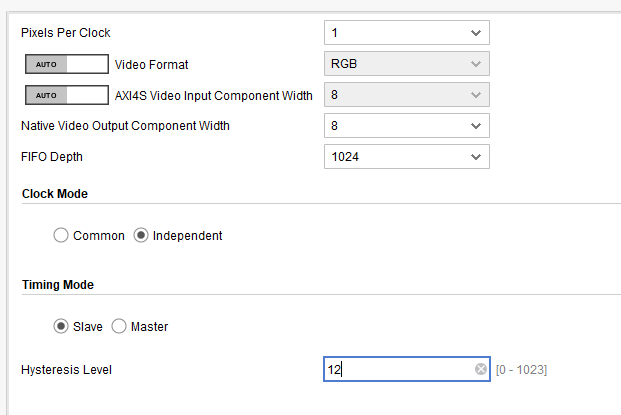

Konfiguration des AXI4-Stream to Video Out Blocks:

Der AXI4-Stream to Video Out IP-Core kombiniert die Steuersignale aus dem Video Timing Controller mit dem Datenstrom aus dem AXI-Stream Interface des Video DMA um die Bilddaten und den benötigten HSync, bzw. den benötigen VSync zu erzeugen.

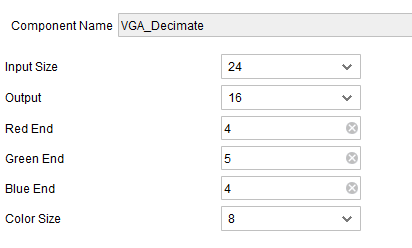

Konfiguration des VGA Decimate Blocks:

Der VGA Decimate Block hat die Aufgabe das Videosignal des AXI4-Stream to Video Out Cores zu reduzieren, da das ZYBO nur 16-Bit Videosignale verarbeiten kann und der AXI4-Stream to Video Out Block mindestens ein 24-Bit Signal ausgibt.

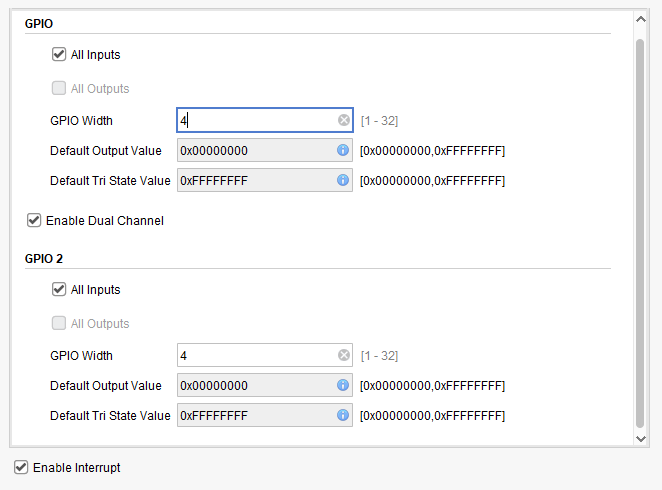

Konfiguration der AXI GPIO:

Über die Schalter und Taster des ZYBO werden mit Hilfe des AXI GPIO die Bildschirmauflösung und der Ausgabemodus eingestellt. Dazu werden zwei 4-Bit Eingangskanäle und der Interruptausgang des IP-Cores benötigt.

Damit ist das Design vollständig. Weiter gehts mit dem ersten Teil der Software…

→ Zurück